Vivado関係のTips

Xilinxの開発ツールVivado関係の自分用メモ

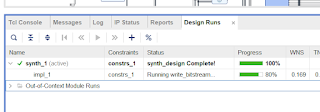

SYNTHESISやIMPLEMENTATIONの進捗具合を%表示で確認する

画面下部のDesign RunsタブのProgressに進捗具合が%で表示されている。

もしDesign RunsタブにProgressが表示されていなければ、NameとかConstraintsとかStatusとか書いてあるバー上で右クリックしProgressにチェックを入れれば表示される。

0%からの進みが明らかに遅いし、75%からいきなり100%になったりするので全くあてにならないが、少なくとも動作に進捗があることは確認できる。

ブロックデザインで配線全体を消さずにとあるピンだけ接続を外す

配線から切り離したいピンの上で右クリックしDisconnect Pinをクリックする。そのピンだけ配線から切り離される。

知らないと地味に作業が大変。

ブロックデザインで拡大縮小、スライド移動する

Ctrlキーを押しながらマウスのホイールを回すことでzoomモードにせずとも拡大縮小ができる。

またctrlキーと左クリックを押しながらマウスを動かすと、デザインの画面をスマホ画面のようにスワイプできる。ただしIPの上でctrlキーを押して左クリックしながら動かすとIPを複製してしまうので注意が必要。

Vivadoプロジェクトファイル移動後などにエラーが消えない

Vivadoプロジェクト移行後などに[IP_Flow 19-993] Could not find IP file for IP 'TEST_IP_util_vector_logic_4_0'.といったようなエラーが発生することがたまにある。

ブロックデザイン中に自作IPなどを組み込んだプロジェクトを移動させたりした後に発生することが多い気がする。これが発生するとsynthesisが通らない。

該当のプロジェクト名\プロジェクト名.srcs\sources_1\bd\ブロックデザイン名\ipの中身を消した後Vivadoを再起動する。

再起動後ブロックデザインを開こうとすると消したファイル群を生成しなおしてかなりの時間(数分~十数分)待たされるがエラーが出なくなる。

Synthesis時にdefault_nettype is noneが出てコンパイルに失敗する

[Synth 8-6735] net type must be explicitly specified for 's_axi_AXILiteS_AWVALID' when default_nettype is none というようなエラーが出てしまうことがあった。

エラー箇所のファイルはVivadoHLSが自動生成したファイルなのに何でエラーが出るんだ?と悩んだ。しかもすぐにエラーが出るのではなく十数分後とかに出る。

自分で追加したVerilogべた書きのRTL回路の記述の先頭にwire宣言なしではコンパイルエラーになるようにするポカヨケのおまじない「`default_nettype none」が記載されていたのが原因だった。

このせいでwire宣言なし(暗黙のwire宣言)で作られているVivadoが自動生成したファイルやIPにもポカヨケチェックが入ってしまいエラーが出てしまったようだ。

おまじないを書いたRTL回路のコンパイル後にこのエラーは発生するため、コンパイルされる順番によってエラーの出る箇所が毎回違うのにも納得がいった。

単純に「`default_nettype none」を消すか、「`default_nettype none」を書くときはそのファイル末尾に「`default_nettype wire」も記載しておくことで防止できる。

0 件のコメント:

コメントを投稿