VivadoのIPにはVIO(Virtual input output)というものがあります。

これを使えば、FPGA書き込み後PCからI/Oを叩いたり値を覗いたりできます。

とりあえず、今回はVIOからZYBO

Z7上のLEDを叩く・スイッチを覗くを行ってみます。今回RGBLEDも光らせてますが、たしか無印ZYBOにはRGBLEDが実装されていなかったと思います。無印ZYBOを使う場合はRGBLEDは省略してください。

まずはVIOからアクセスするだけなのでRTLソースは一切いりません。プロジェクトを作成したら、ブロックデザインを作ります。

まずはVIOを追加します。

追加されたVIOのアイコンをダブルクリックしてRe-customize IPを開きます。Input Probe CountはInput(覗くほう)のバスの数、Output

Probe Countは Output(叩くほう)のバスの数です。Enable Input Probe Activity Detectorsにチェックを入れるとInputに変化があったとき覗いている値を自動で更新してくれます。今回はZYBO上の4つのスライドスイッチを4bit幅の1つのバス、プッシュスイッチをそれぞれ1bit幅の4つのバスとして合計5つのInputバスを用意。またRGBLEDのLD5を3bit幅の1つのバス、LD0~LD3までをそれぞれ1bit幅の4つのバスとして合計5つのOutputバスを用意しました。

PROBE_IN Ports、PROBE_OUT

Portsのタブで各バスの幅を決められます。

OUTのほうはInitial

Valueに初期値も決められます。

Re-customize IPをOKを押して閉じたら、VIOの各ポートを外に出してやります。

ここではクロックはK17につながっている125MHzを利用するのでclkのポート作成時は周波数を125MHzに変えておきます。(多分変えなくても動きますが、念のため)

保存してCreate HDL Wrapperでブロックデザインのラッパーを作成し、Run Synthesisだけして、ピンアサインを設定します。

基本的に全部(clockも)LVCMOS33です。下記のようにポートを接続します。

ZYBO は125MHzのクロックがK17に入力されているため、これを利用できます。ブロックデザインにzyboのPSを追加してそのクロックを使う方法もありますが、それだと接続もめんどくさいし、動作させるたびにSDKから適当なプロジェクトを動かしてPSを動作させてやらないとクロックが出てきません。

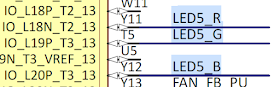

回路図を見るとZ7以降についているRGBのLEDのLD5はREDがY11、GREENがT5、BLUEがY12に接続されています。

ピンを決めてxdc(ピンアサインなどの規約を保存するファイル)を保存したらGenerate Bitstreamでbitファイルを生成します。

BitファイルができたらZYBOをPCに接続して、Open Hardware ManagerでHardwareManagerを開いてbitファイルを書き込みます。(ZYBOのJP5がJTAGになっていることを確認して)

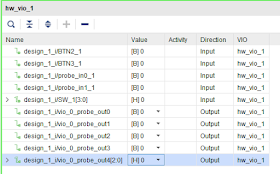

書き込み終わって書き込み完了を示すZYBO上のLD2(DONE)が緑に光ると同時くらいにvivadoのDashboards Optionsにhw_vio_1というウィンドウが開きます。

hw_vio_1の+マークをクリックすると、ブロックデザインで追加したVIOのProveが表示されます。

とりあえず全部叩いたり覗いたりしたいので全部選択して追加しました。

試しにボタンを押したりしてみると、Inputは自動で検出し値を表示してくれます。Valueが値、Activityが立ち上がりか立下りのエッジを検出したことを示します。

OutputはValueの値をタブで変えるか入力すると叩いてLEDを光らせることができます。

VIOを使えば簡単にPC上でI/O制御ができるので、デバッグや動作確認に便利です。

ちなみに回路規模はこんな感じでした。

0 件のコメント:

コメントを投稿