前回はLEDが一つしか点滅しない回路でしたが、今回はブロックデザイン機能を使って前回の回路を複数用意して、複数のLEDを光らせてみようと思います。

ブロックデザイン機能を使うので今回はRTLの編集は一切行わずGUI(画面上)で線をつなげたり、回路を追加するだけで直感的に回路作成ができます。

通常同じ回路を複数つなげたい場合はラッパーを作ってインスタンスしてやらないといけないですが、ブロックデザインならそれをブロック図を見ながら作成できて配線も自動でやってくれてラッパーファイルも作ってくれるので大変便利です。(僕の知る限り)アルテラのQuartusにはそういった機能もなくQsysも使いにくかったので大変助かっています。

前回のプロジェクトをそのまま使って進めていきます。

ブロックデザインプロジェクトを作成する

Flow NavigatorのIP INTEGRATORのCreate Block Designをクリックします

Design nameは任意のものに変更できますが、めんどくさいのでデフォルトのままでOKをクリックします。(なぜかわからないけど、いろんな書籍やサイトや知り合いは皆Design

nameをそのままにして使っている人が多い気がする。プロジェクト名はちゃんとつけるのに)

数秒でブロックデザインが作成されます。

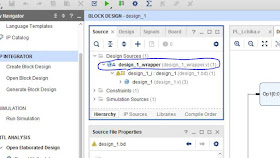

Sourcesを見てみると、design_1が追加されているのがわかります。

右側のDiagramのところで回路をぺたぺた作成していきます。そのままだとDiagramウィンドウが小さくて見にくいので、右上のfloatボタンを押してウィンドウを独立させましょう。

IPやRTLをブロックデザインに追加する

Diagramウィンドウ内で右クリックして、Add Module…をクリックします。

前回作成したRTLが表示されるので、それを選択し、OKをクリックします。

RTLが追加されました。

同様にAdd Module…でLチカ回路をもう一つ追加します。

せっかくなので標準のIPも追加して片方のLEDの点滅タイミングを反転しましょう。

ウィンドウ内で右クリックして、Add IP…をクリックします。

Utility Vector Logicをダブルクリックしてロジック回路のIPを追加します。

ロジック回路が追加されましたが、ANDの回路になっています。

Diagram上のIPをダブルクリックしてロジック回路をカスタマイズします。

C_SIZEを1にC_OPERATIONをnotにします。

DiagramのIPの形がANDからNOTに変わったと思います。

配線と外部端子(ポート)を作成する

Res[0:0]と片方のLチカ回路のclkをつなぎます。接続したい端子の上でカーソルが鉛筆マークになったらもう片方のつなぎたい端子までドラッグ&ドロップするとつなげます。ちなみにDiagramのウィンドウのRegenerate Layout(更新マーク)をクリックすると回路の接続自体はそのままで自動でいい感じに並び替えてくれます。

外部接続端子を作ります。端子をクリックし端子だけオレンジになって選択されている状態にして右クリックし、Make Externalをクリックします。

以下の図のように外部端子を出して、配線をつなぎます。clkのところの分岐は、先にどちらかをMake Externalしてからもう片方から配線をつなげばできます。

もしくは何も選択していない状態でDiagram上で右クリックしてCreate Portをクリックすることで外部接続端子を作れます。

Portnameに任意のポート名、Directionに入出力方向を入力します。Typeがよくわからないのですが、Otherのままで大丈夫です。

ウィンドウの右上のDockをクリックして、一度ウィンドウを元の場所に戻します。

現在選択中の各ポートやモジュールの名前などは右側のPropertiesに表示されており、名前の変更もそこでできます。

回路をつなげ終わったらCtrl+Sもしくは左上のフロッピーディスクマークをクリックしてブロックデザインを保存します。

ラッパーファイルを作成する

Sourceのdesign_1を右クリックして、Create HDL Wrapperをクリックします。

Let Vivado manage wrapper and auto-updateを選択して、OKをクリックします。

ラッパーファイルが作成されました。もしブロックデザインを変更した場合は再度Create

HDL Wrapperする必要があります。

ピン制約を設定する

まずFlow NavigatorのRTL ANALYSISのOpen Elaborated

Designをクリックします。上のほうにElaborated Design is

out-of-date.と書かれたところにReloadがあるのでそこをクリックします。PCによっては数分かかります。これでラッパーファイルが読み込まれて、ピン制約を決めることができます。

I/O Portsタブが出現したらピン制約を決めます。

I/O StdはすべてLVCMOSS33にして、clk_0はK17、led_0はM14、led_1はM15にPackage Pinを設定し、保存します。

ジェネレートして書き込む

ピン制約が終わったら、あとはBitstreamファイルを生成して書き込むだけです。

Generate BitstreamをクリックしてBitstreamファイルを生成します。

僕の非力なPCでは数分かかりました。

Open Hardware ManagerをクリックしてBitstreamをZYBOに書き込んでLチカさせましょう。JP5をJTAGにするのを忘れずに。

ZYBO上のLD0とLD1が交互にチカチカすると思います。

ということで今回はブロックデザインだけでRTLは一切書かずに複数のLEDをチカチカさせました。かなり直感的に回路を作成することができるのを体感できたと思います。

0 件のコメント:

コメントを投稿